本文旨在介绍使用 NXP i.MX RT1170 时,在需要外挂 SDRAM 的情况下,Layout 上的一些细节以及注意事项;

首先先简单介绍一下 SDRAM,这是一种很常见的高速记忆体,但它的性能和可靠性会直接影响到装置的运行速度和稳定性。

在进行 SDRAM 的设计时,Layout 是非常重要的一个环节。一个好的 Layout 设计可以保证 SDRAM 的性能和可靠性,而一个不良的 Layout 设计则可能导致 SDRAM 的性能下降、资料传输错误、EMI 过高等问题。因此,在进行 SDRAM 的 Layout 设计时,为了确保设计的成功,有一些重要的注意事项。

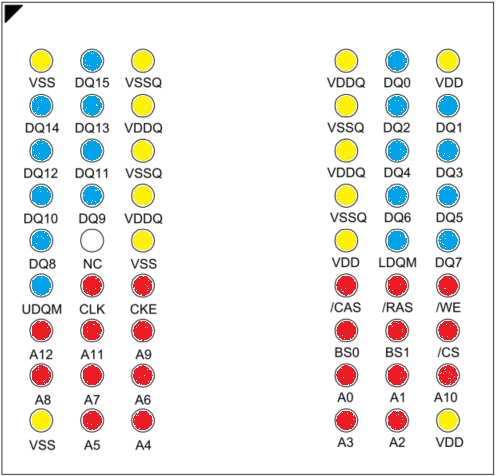

二. SDRAM Pin 介绍

以 Winbond 的 W9825G6KB 16 Bits SDRAM 为例,它的 PIN 可以分为以下三类,不同类型的 Pin 在 Layout 时有不同的注意事项:

1. Power PIN ( 黄色 ):包含 VDD、VSS、VDDQ、VSSQ,

*VDDQ 和 VSSQ 为驱动 Pin 脚的电源 & 地

2. Control PIN ( 红色 ):包括 CLK、CS、RAS、CAS、WE、BA 和 A0-A11,这些 PIN 用于控制 SDRAM 的操作。

*CS 是 Chip Select,用于选择 SDRAM ( 使用复数 SDRAM 时 )

*RAS 和 CAS 是 Row Address Select 和 Column Address Select,用于选择存取的记忆体位置,并将其读取或写入

*WE 是 Write Enable,用于决定此次操作是读取或写入

*BA 是 Bank Address,用于选择 SDRAM 中对应的 Bank

*A0-A11 是 Address 输入,用于指定要操作的 SDRAM 位址

3. Data PIN ( 蓝色 ):包含 DQ0-DQ15 和 DM0-DM1,这些 PIN 用于传输实际的资料

*DM0 和 DM1 是 Data Mask,用于指示哪些资料位是有效的。

三. Layout 重点

1. 在 SDRAM 的 Layout 中,电源系统是非常重要的一个部分,关系到装置的稳定性和可靠性,提供 SDRAM 的 Power Pin 足够的电才能保证其正常启动和运作。

在整个系统中,首先需要关注的是总共需要多少的电流才能驱动,必须确保源头有足够的供电,否则连 SDRAM 都开不起来就更别提后续了。

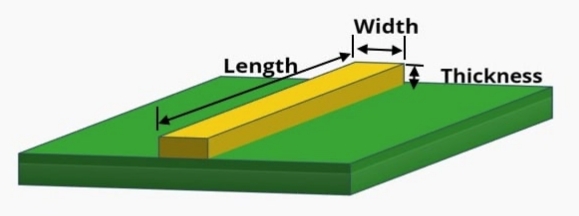

确认了供电之后要怎么把电导入 SDRAM 呢?答案是透过 Trace 和 VIA,Trace 是指 PCB 上的线路,VIA 是指 PCB 上的贯孔,两者皆为铜箔,可导电;

但是当 Current 流过时,由于有直流阻抗的存在,部分电流会被耗损并转换成热,导致温度上升,甚至是过热的情况产生,因此有两点需要确认;

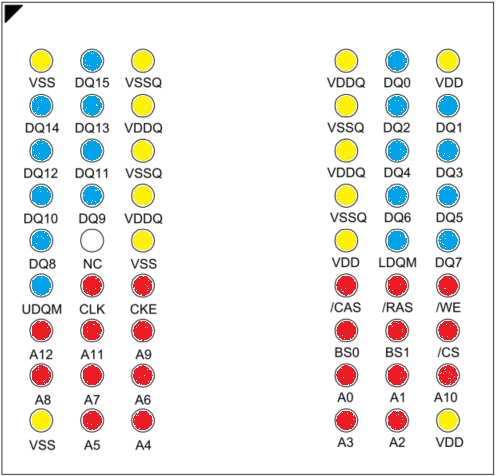

Trace 的载流能力,取决于走线的厚度、宽度和可以容忍的温度上升

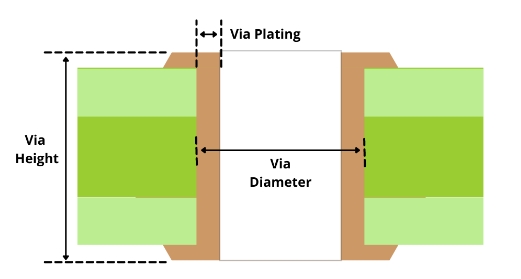

VIA 的载流能力,取决于孔的内壁厚度、内径宽度、高度和可以容忍的温度上升

具体计算公式如下:

I = K△T0.44A0.725

I = 载流能力,能通过多少的电流 ( 安培 )

K = 校正常数,在内层取 0.024,在外层取 0.048

T = 通电后相比于原始温度提升的温度,如 5 代表原本 25°C 通电后变成 30°C

A = 电流通过的截面积,Trace = 走线的宽度 x 厚度,VIA = π ( 孔外径2 - 孔内径2 )

注:尽量不要使用到理论上的最大电流量,保留一些馀裕,例如只抓八成。

铺铜的厚度和宽度会影响 PCB 的载流能力,简单说相同环境条件下越多铜能流过的电流就越大。

2. Control 和 Data Pin 则都需要先进行 controlled impedance ( 阻抗控制或称阻抗匹配 ),

阻抗匹配是指在设计电路时,将信号源的阻抗和目标的阻抗调整到相等或相近的状态,以确保信号能够稳定地传输,适当的调整可以减少信号的反射、失真和能量损失;在 PCB 设计中可以透过调整 PCB 的叠构和线宽来达成。

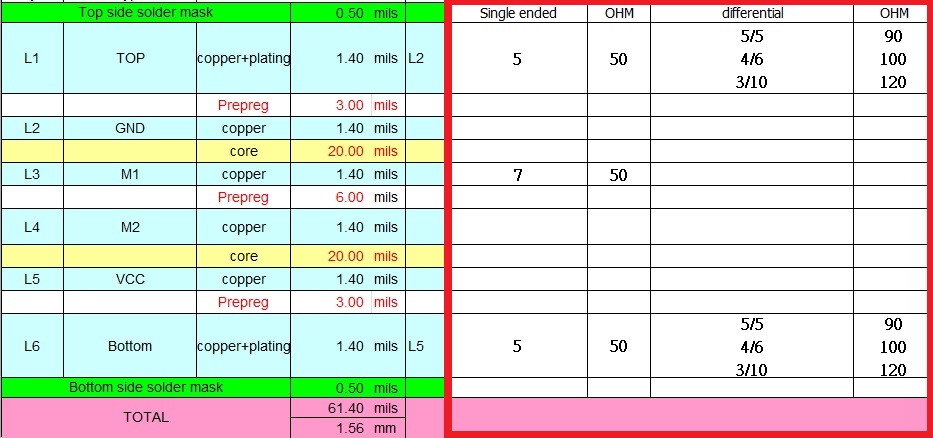

以 SDRAM 为例,根据 Datasheet 需要 50Ω 的 single-ended traces controlled impedance,将此需求提供给制板厂后会收到一张类似下方的叠构建议,可以看到红框左侧是 Single-ended,下方的数字是走线的线宽 ( mil ),旁边则是阻抗,代表在 Top 或 Bottom 层走 5 mil 的线会得到 50Ω 的 controlled impedance,在 M1 层则须达到 7 mil;红框右侧 differential 下方的数字则是代表 线宽/线距,代表在 Top 或 Bottom 层走 5mil 的线,两条 differential pair 的线距保持 5mil,可以得到 90Ω 的 controlled impedance;具体可以参考下方示意图;不同的高速讯号都会有不同的阻抗要求,在向制板厂询问时需一并提出需求 ( 须先决定各个高速讯号分别要走在哪一层,才能在对应的层透过叠构调出需要的阻抗 )。

3. 接着要进行等长处理,等长处理是指在 PCB 设计中,将信号线的长度设计成相等的长度,以避免信号在传输过程中产生反射和干扰,同时确保信号的稳定性和可靠性。

举个例子:MCU 同时在 8 条 Data 线上送出 High,结果因为每条线的长度落差太大,High 讯号到达的时机有快有慢,导致 SDRAM 取值时原本应该全是 High,结果变成有 High 有 Low,传送的 Data 变成错误的。

故类似 SDRAM 这种高速讯号,一起传值的 PIN 要进行等长处理;又因为资料的计量单位为 1Byte = 8Bit,故根据这个观念可以把剩馀的 PIN 拆成以下三组:

第一组:Data0~Data7 + DM0 ( 1 Byte + Data mask )

第二组:Data8~Data15 + DM1 ( 1 Byte + Data mask )

第三组:Control Pin ( CLK、CS、RAS、CAS、WE、BA 和 A0-A11 )

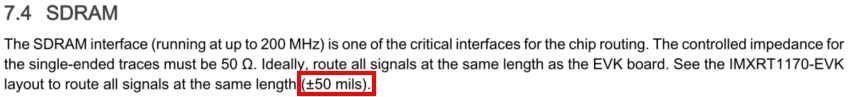

每组线个别进行等长处理,详细的线长差允许值可以参考各自的 Datasheet 或是 Hardware Designed Guide,以 MIMXRT1170 的 Hardware Development Guide 为例,有提到每组线的长度差要控制在 50 mil 以内,如下图,

即每组线中最长减最短要小于 50 mil。

4. 在进行 SDRAM 走线时,需要注意参考层 ( 平面 )。

参考层是指最靠近走线的另一层,作为信号传输的参考点,提供阻抗和电流回流路径。通常,参考层是 GND 或电源层。这样可以减少信号传输中的干扰和杂讯,提高信号的稳定性和可靠性。

如 SDRAM 这样的高速讯号需要确保参考层的连续性,如前文所提到,高速讯号需要进行阻抗控制以保持整组讯号的同步性,参考层如果有变化会导致阻抗跟着有变化,进而造成阻抗不连续,将会导致信号的传输中断、失真和干扰,进而影响整个系统,故其走线下方的参考层不可被切割也不可有其他走线;同时根据上文提到的,为了保证每组讯号的传输条件可以一致,同一组线的参考层要始终保持一致,同一时间不要有的线参考 GND 层、有的线参考 VCC 层,如果需要切换参考层则整组线一起切换。

更多的细节和实际范例可以参考本系列的其他文章

四. 参考资料

- Hardware Development Guide for the MIMXRT1160/1170 Processor

- Winbond W9825G6KB Datasheet

评论