一.概述

主控 MCU LPC5516是一款基于 Arm Cortex-M33 的嵌入式微控制器,运行频率高达 150MHZ,包括以下功能:

- 高达 96 kB 的片上 SRAM。

- 最多 256 kB 片上闪存。

- 高速/全速 USB 主机和具有全速无晶操作的设备接口。

- CAN-FD。

- 五个通用定时器。

- 一个 SCTimer/PWM。

- 一个 RTC /报警计时器。

- 一个 24 位多速率定时器 (MRT)。

- 一个窗口看门狗定时器 (WWDT)。

- 代码看门狗

- 高速 SPI (50MHz)。

- 8 个灵活的串行通信外设(每个外设都可以是 USART、SPI、2C 或 12S 接口)。

- 一个 16 位 ADC 能够同时转换。

- 温度传感器。

二. 原理图

关于 LPC5516JBD100 原理图设计内容如下:

1. 电源与时钟输入

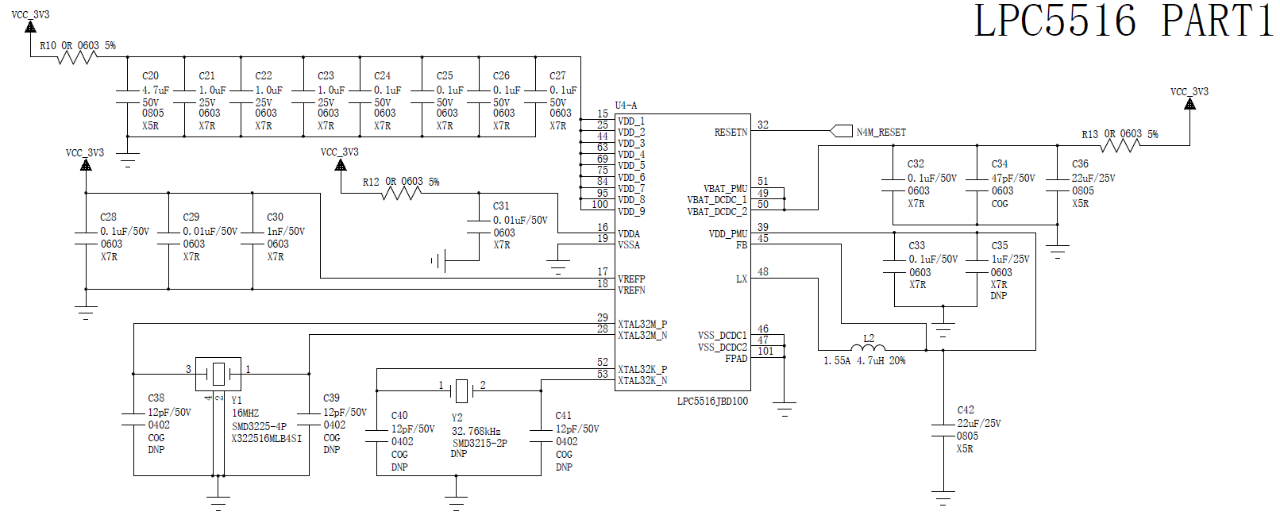

图 1 电源与时钟输入

如图 1 所示为 LPC5516JBD100 电源与时钟电路参考设计,其引脚功能及设计注意事项如下:

(1)LPC55xx 系列需要 1.8V 至 3.6 V 的工作单电压电源,对于 LPC5516JBD100 供电电压为 3.3V 左右。

(2) VREFP、VREFN 引脚是 ADC 的正参考电压和负参考电压输入,在原理图设计时为滤除更多噪声可在输入前增加几个电容,取 10 倍差值。

(3) LPC5516 晶振电路工作频率为 16 MHz 或 32 MHz,XTAL 引脚为外部晶振输入,如果选择外部时钟输入,在确定晶振型号后还需要计算晶振匹配电容。例如当选择 16MHz X322516MLB4SI 晶振,由 datasheet 可知 X322516MLB4SI 晶振负载电容 CL 为 9pF,根据负载电容 CL 计算出匹配电容(晶振):C38=C39=2 *(CL-CS),其中 Cs 为分布电容,一般为 1~5pF。最终计算得匹配电容范围 8 ~ 16pF,在 LPC5516 Datasheet 中描述,匹配电容小于 20pF 时,可以选择不进行贴片,当选择其他型号的晶振计算得出的匹配电容大于 20 pF 时,则需焊接上匹配电容。同样对于工作频率为 32. 768 kHz 的晶体振荡器,也可选择外部时钟输入,匹配电容值计算方式与上述一致。

(4) LPC5516 内部核电压由内部 DC/DC 稳压器提供,如图 2 所示:VBAT_DCDC 及 VBAT_PMU 引脚是内部 DCDC 稳压器电压输入引脚,连接外部电源为内部 DCDC 稳压器提供输入;LX 是内部 DCDC 变换器功率级输出,经过外部电感和两个或三个电容,进入核供应引脚 VDD_PMU 进行供应,电压为 1V;FB 引脚则是 DCDC 变换器反馈节点(稳压输出)。在使用内部 DCDC 转换器时,其电容电感按照 datasheet 来取值,其典型电路图如下。

图 2 使用内部 DC-DC 转换器

图3 USB 下载

如图 3 为 LPC5516JBD100 USB 下载电路参考设计,当原理图设计时可参考以下事项:

(1)在 USB 母座的 VBUS 引脚上增加滤波磁珠,可滤除输入电源上的干扰。

(2)在 USB 线上放置静电放电(ESD)保护器件,可为高速数据传输应用的 IO 端口提供保护。

(3)USB1_DP 及 USB1_DM 为 USB1 差分信号的输入引脚,Layout 时需要按差分信号布线,可预留两个 0Ω 电阻方便阻抗匹配。

具体的型号及封装需按实际设计进行选择,当未使用 USB 下载电路时,信号输入引脚悬空。

3. 连接引脚

图 4 连接引脚

LPC5516 除特定引脚具有特定的功能,无法另外配置外,其余 IO 可通过软件进行修改。

(1)LPC5516JBD100 有 64 个通用 GPIO ,通过软件配置可配置为不同功能。

(2)包含了 9 个串行外设(Flexcomm Interface 0-7和Flexcomm Interface 8),每个Flexcomm Interface(除了专用于高速 SPI 的 Flexcomm 8) 都可以通过软件选择为 USART、SPI、2C 和 I2S 接口。

(3)有一个 16 位 ADC ,具有 5 个差分通道对(或 10 个单端通道),以及具有多个内部和外部触发, 输入和采样率高达 2.0 MSamples/sec。在属于一个差分对的 2 个 ADC 输入通道上,ADC 还支持同时转换。

4. ISP 与 RESET

图 5 ISP 与 RESET

(1) RESET 引脚需进行上拉,防止一直处于复位状态导致无法使用。

(2) ISP 启动电路可添加上拉电阻,默认进入被动启动模式,如果 ISP 为低电平则会进入 ISP 启动模式。

三. 关于 MCU PCB Layout 建议

- 所有去耦电容应尽可能放置在靠近各自电源引脚的位置。

- 去耦电容的接地侧应有一个通向焊盘的过孔,该过孔直接向下连接到内部接地层。

- 将 PCB 上的晶振和外部负载电容尽可能连接到靠近芯片振荡器输入和输出引脚的位置。

- 振荡电路中的走线长度应尽可能短,不得与其他信号线交叉。

- 确保匹配电容具有公共接地层。

- 振荡电路环路必须尽可能小,最大限度地减少通过 PCB 耦合形成的噪声,并保持尽可能小的寄生效应。

- 多层 PCB 的晶振电路下不要布置其他信号线。

四. 总结

本文介绍了 LPC5516 原理图设计内容及 Layout 的注意事项,意在为读者使用芯片时提供参考,希望有所帮助。

五. 参考资料

1. Hardware Design Guidelines for LPC55(S)xx Microcontrollers

2. LPC55S1x/LPC551x User Manual

3. LPC 55S1x/LPC551x Data Sheet

评论