一、 前言

G9Q 系列处理器是专为新一代车内核心网关设计的高性能车规级汽车芯片,采用双内核异构设计,包含一个高性能的 Cortex-A55 CPU 内核,一对双核锁步的高可靠 Cortex-R5 内核,在支持多种外设接口,包括两个 PCIe3.0接口,两个 USB3.0 接口, 两个支持 TSN 的千兆以太网接口,以及多达 20 个 CAN-FD 接口和 16 个 UART 接口。承载未来网关丰富的应用同时,也能满足高功能安全级别和可靠性的要求。

二、SEMIDRIVE G9Q USB 接口电路设计要点

① G9Q 包含 2 个 USB3.0 接口,可以用作 USB Host 或者 USB Device,也可以同时向下兼容 2.0 模式,可以支持或仅支持 USB2.0 的设备。

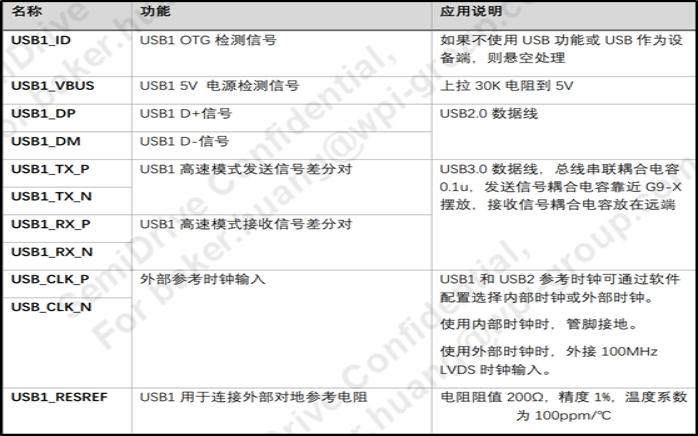

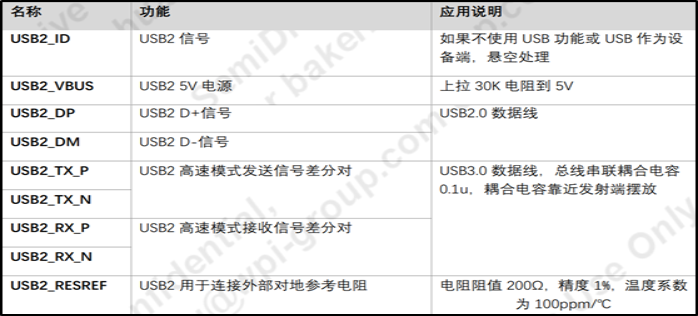

② 下图是 USB1 和 USB2的管脚介绍,默认 USB1 这一路作为系统升级使用,USB2 可用作与其它设备或模块通信连接使用

▲ 图 1 USB1 引脚描述图

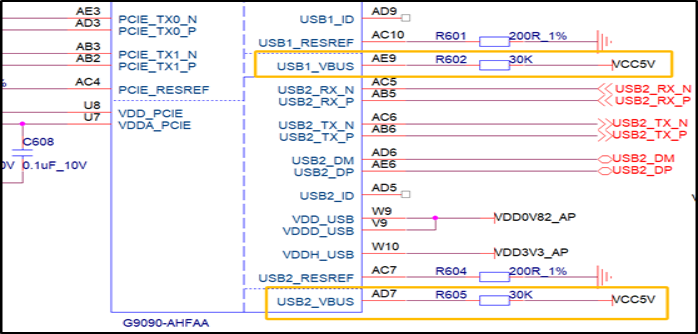

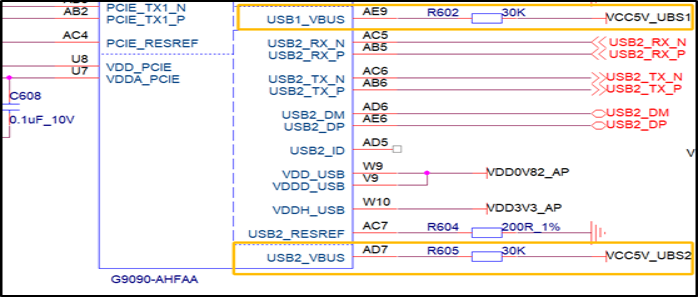

③ 在之前的 DEMO 板 USB 接口电路设计中,芯片的 USB1_VBUS 和 USB2_VBUS 引脚是上拉 30K 电阻到 VCC5V,这是一种比较简单的做法,我们不推荐产品在实际生产中采用这种方法。

▲ 图 3 USB1_VBUS & USB2_VBUS 连接图

④ 我们建议芯片的 USB1_VBUS 和 USB2_VBUS 引脚在实际电路设计中,通过上拉 30K 电阻到 USB 接口的 VBUS电源信号上。当 SoC 做 Device 模式时,由外部 USB 线提供 VBUS 的电压,触发芯片 USB 模块的工作。当 SoC 做 Host 模式时,由可控电源输出 VBUS 电压,同时提供内部检测和对外供电。这样的好处是可以避免出现和外部 Device连接异常的问题。

▲ 图 4 推荐 USB1_VBUS & USB2_VBUS 连接图

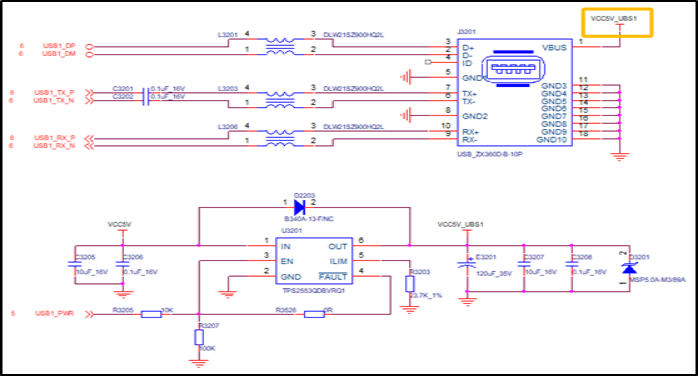

▲ 图 5 USB1 接口电路图

⑤ USB2.0 & 3.0 差分、数据线按 90Ω 阻抗设计,差分线误差按 5mil 设计,遵循标准的高速差分路由规则,保证信号的完整性。

⑥ USB 信号线应远离晶振、感性设备、PCIE 和 RF 信号等。如果信号需要换层,需要两个地孔同时跟着 TX_P/N,RX_P/N。

⑦ 如果使用 ESD 元件,请将 ESD 保护元件尽量靠近 USB 接口,注意 ESD 保护元件的结电容对 USB 数据线的影响。一般情况下,对于 USB2.0 的 ESD 电容值应小于 2pF,对于 USB3.0 的 ESD 电容值应小于 0.4pF。

以上便是芯驰 SEMIDRIVE G9Q USB 接口电路设计要点。

接下来我们也会不断更新更多关于 SEMIDRIVE X9、G9 系列的开发博文,同时我们也会持续推出更多 ADAS 相关的技术开发博文。如需更深入的技术交流,欢迎在博文下方评论或者关注并给我留言。

附录:参考文献

①《 G9X 处理器硬件设计指南_Rev0.9.2 》

②《 SD004_G9X_REF_A03_SCH 》

③《 G9Q 处理器数据手册_Rev04.03 》

评论