一、与启动相关的项目检查

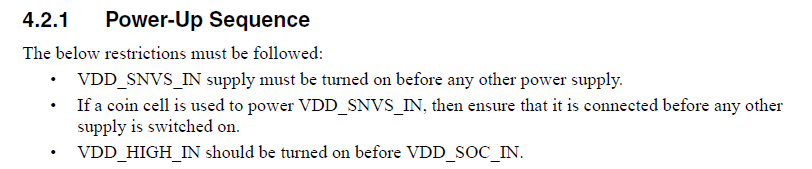

1.上电时序

上电时序对i.MX6UL芯片至关重要。不正确的上电时序可能导致芯片启动失败或者功能异常,严重的会导致芯片的ESD损坏。请确保上电时序满足如下的顺序要求:

a. 请确保SNVS_IN第一个上电,任何其它i.MX6UL的供电不能在SNVS_IN稳定之前上电,任何i.MX6UL的IO管脚都不能在SNVS_IN稳定前出现高电平。

b. 请确保其它供电在SNVS_IN稳定后至少1ms后再上电。

c. VDDHIGH_IN不可以直接和SNVS_IN短接在一起。

d. VDD_HIGH_IN 应该在VDD_SOC_IN上电之前上电。

e. 请确保POR_B在SNVS_IN上电之前为低电平,且在所有MX6UL的供电, 32.768KHz晶体, 24MHz晶体稳定后再回到高电平。

2.电源纹波

电源纹波的控制对于i.MX6UL的稳定运行至关重要,i.MX6UL对于电源纹波的要求是p-p(峰-峰值)控制在5%以内,以VDDARM_CAP 为例,如果设置的输出电平为1.2V的话,那么纹波p-p要控制在60mV以内。要控制好电源纹波,请遵从如下规则:

a. BUCK电容(22uF或10uF)和去耦电容(22uF或0.1uF)的数量和容值的配置请严格参考最新的NXP i.MX6UL EVK板的参考原理图。 或者参考 IMX6ULHDG.PDF:

Table 9. Power supply decoupling recommendations

b. 22uF电容请尽可能靠近相应的电源PAD来摆放。

c. 22uF or 0.1uF的电容请分散靠近相应的电源PAD摆放。

3.复位与时钟

a. POR_B复位信号的时间要求。确保POR_B在SNVS_IN上电之前为低,并在所有电源, 32.768KHz 晶体, 24MHz晶体都稳定后才能

释放(由低变高)。

b. 32.768KHz 晶体的电容配置,请使用以下近似公式选择负载电容的配置:

2× Cload - 3~5pF

注:- Cload为晶体手册上标明的值,请注意,同一种型号可能会有几种不同的负载电容指标,请确认实际使用的是其中的哪一种。

- 3~5pF是估算的板级衍生电容。

- 例如,一个标明为7pF负载电容的晶体,实际的板级设计电容应为:

2× 7 - 3~5=9~11pF, 因此建议使用10pF在板电容。

c. 24M晶体需要在XTALI加2.2Mohm的下拉电阻。

d. 32.768KHz与24MHz晶体不要外接任何并联偏压电阻, i.MX6UL芯片内部已经具有。

e. 32.768KHz晶体的选择请遵从如下规则:

• 内部等效电阻ESR 最大不能超过100K。

• 最大的驱动功率小于等于1uW。

• 精度50ppm或更好。

f. 24MHz晶体的选择请遵从如下规则:

• 内部等效电阻80ohm的晶体,推荐最大驱动功率不超过250uW。

• 对于内部等效电阻为50ohm的晶体,推荐最大驱动功率不超过200uW。

• 精度50ppm或者更好。

4.其它注意事项

a. eMMC 启动模式选择。

注:如果是从eMMC启动,启动模式请不要配置为DDR mode,要使用SDR模式。

请参看BOOT_CFG2[7,6,5]

b. BOOT_CFG4[7] 启动设置管脚 infinite 模式选择。

请确保这个管脚在启动时处于下拉的状态。

c. 请确保TEST_MODE 信号下拉到GND。

d. 请确保NGND_KEL0信号直接接地(GND)。

二、与电源相关的项目检查

电源管脚电路设计注意事项:

a. 各组电源的电容数量与容值配置请严格参考我们的官方原理图。

b. 不要连接任何外部的负载在如下MX6UL的内部LDO输出上,这些电源是给i.MX6UL内部供电的:

VDDARM_CAP,VDDSOC_CAP, NVCC_PLL,VDD_SNVS_CAP,VDDUSB_CAP and VDDHIGH_CAP。

三、与DDR相关的项目检查

LPDDR2/DDR3 设计注意事项:

a. DRAM_RESET信号

• 对于DDR3来说, DRAM_RESET信号需要外接10k下拉来满足JEDEC时序的要求。

• 对于LPDDR2/3来说, DRAM_RESET信号的外接10k是不必要的,建议悬空。

b. SDCKE[1:0]信号

•对于DDR3来说, 这个两个信号应该悬空要满足DSM的模式的功耗要求,内部已经有10K下拉。

•对于LPDDR2/3来说,这两个信号需要外接10k下拉来满足JEDEC时序的要求。

c. 确保8组数据线应与对应的DQM和DQS连接在同一组, 例如D0~D7对应DQS0/DQS0_B与DQM0,例如D8~D15对应DQS1/DQS1_B与

DQM1,以此类推。

d. 由于write leveling的要求,请确保DDR芯片与MX6UL芯片的每一组数据线的首位对齐连接,例如,第一组的D0对D0,其它可以任意交换,

第二组的D8对D8, 其它可以任意连接,一次类推。

e. Vref一定不能使用VTT来供电,虽然他们的电压相同。

f. 请确保MX6UL和DDR芯片的ZQPAD外接240 ohm下拉电阻,并确保电阻的精度是1%的。

四、其它注意事项

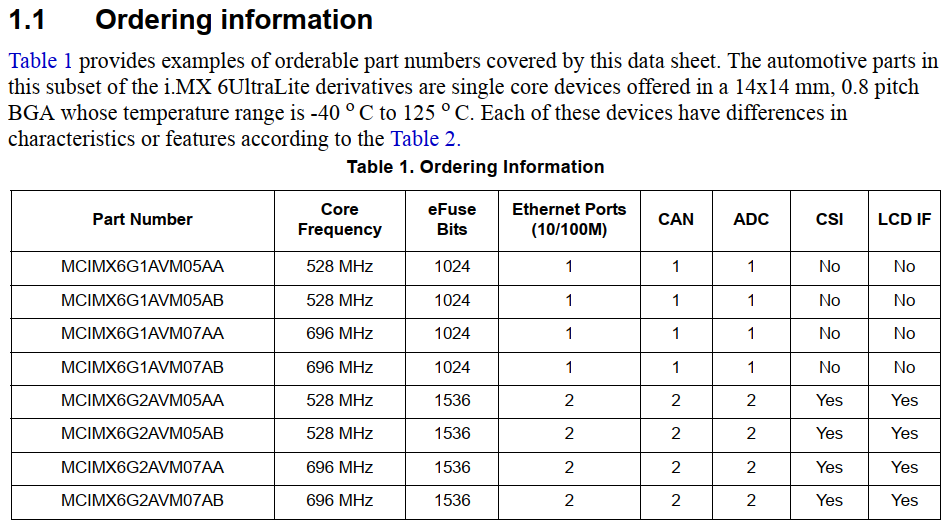

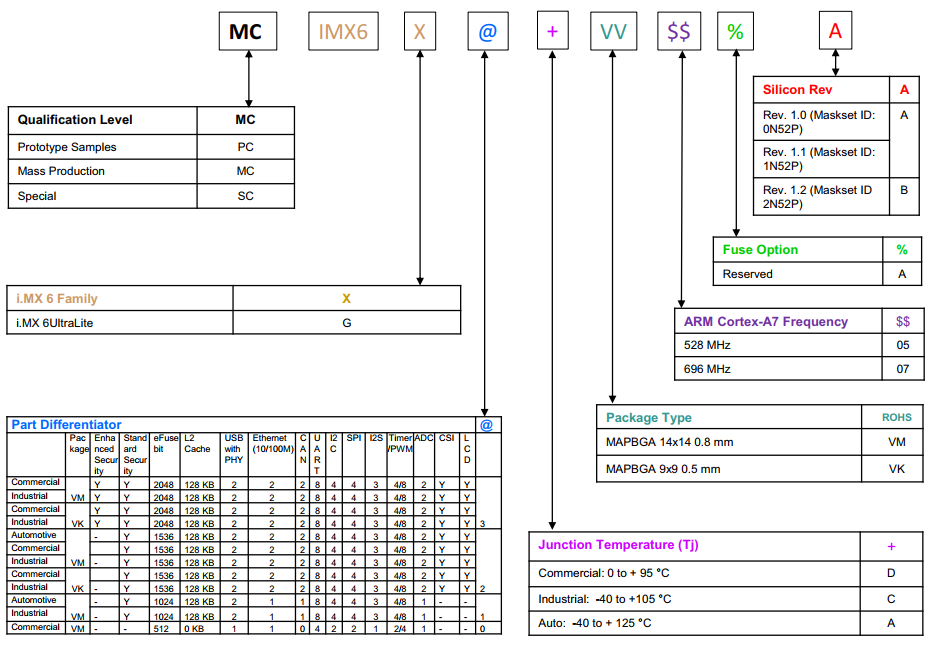

芯片的版本差异

请注意: imx6UL有不同的芯片版本以及不同的封装。

设计时,请务必确认自己的设计是针对哪款芯片的。

具体的差异,请参考 imx6UL datasheet 里的1.1 order information章节。

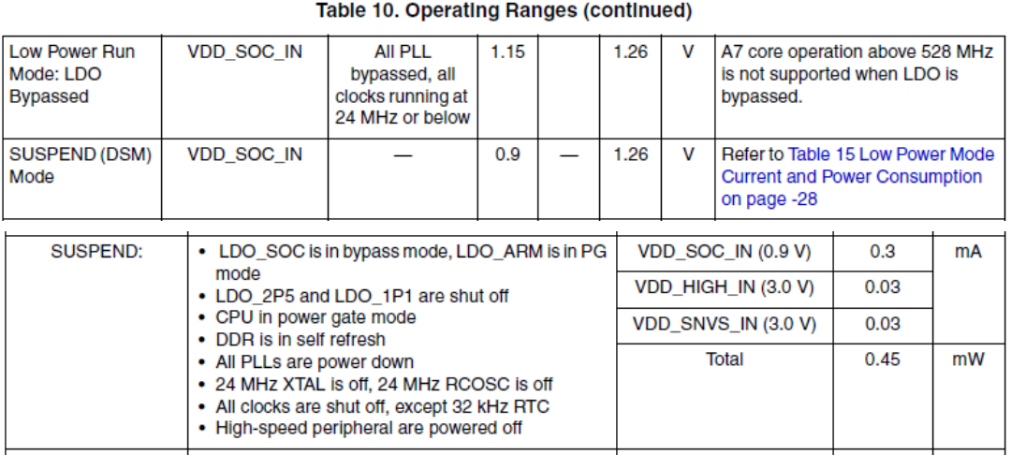

Suspend mode

请注意:在CPU 进入suspend 模式和DSM模式时,内部的LDO将自动进入bypass模式,这时候输入的电压等于输出的电压,所以如果用户在

实际的应用中如果会使用到这两种模式的话,务必需要考虑VDD_SOC_IN电压的控制。

生产模式(manufacturing mode)的设计注意事项:

为了方便用户在产线上通过SD卡下载程序到NAND Flash, eMMC等, imx芯片设计了SD卡的生产模式。

基本工作原理就是:当从指定启动源启动失败时,系统在进入USB 下载模式之前会先检查生产模式设置的SD卡接口,如果能在SD里发现启动image,

那么就会正常从这个SD卡启动。一般来说, SD_CD信号被用来检测是否有SD卡在设定的SD卡端口。

以下是i.MX芯片生产模式支持的SD接口:

- Imx6UL: SD1

- Imx6ULL: SD1

请注意:

- 默认情况下,生产模式是被使能的,并且可以通过 fuse 位DISABLE_SDMMC_MFG 来disable这个功能。

- 不论是否使用这个生产模式,请在SD1_CD信号上加上外部的上拉来保证CD信号的默认高电平。

USB设计注意事项:

a. 根据USB OTG的标准, OTG连接器上的VBUS在板子上电之前需要默认关闭。推荐使用iMX6UL的3V IO电压来控制这个VBUS的输入,确保iMX6UL

没上电之前,这个VBUS不输入到iMX6UL芯片。请参考我们的EVK板设计。

b. USB内部的USB LDO是由USB_OTG1_VBUS 或者USB_OTG2_VBUS来供电的,所以USB模块要正常工作,需要确保其中一个正常上电。

c. 确保在USB接口上设计合适的ESD保护电路,请参考我们的EVK板设计。

d. 确保USB_DP与USB_DM没有接反,我们遇到好几个客户把这两个信号接反从而导致需要重新做板。

e. 当USB信号从imx6芯片到最终的device需要通过好几个连接器时,会严重影响USB信号的质量,需要配合眼图测量调整USB的信号。设计中尽量避免

经过过多的连接器。

I2C设计注意事项:

a. 根据JEDEC标准, I2C上拉电阻的范围是1k~10k,可以根据外设的负载多少来调整,外设越多,则这个值应该越小,推荐如下:

- 接一个外设的推荐值为4.7k,

- 两个外设的推荐值为2.2k。

阻值过小)。

c. 对于PMIC, Touch等对I2C操作频率较高的外设,建议不要使用同一I2C总线。PMIC由于涉及到电源控制,建议使用独立的I2C总线。

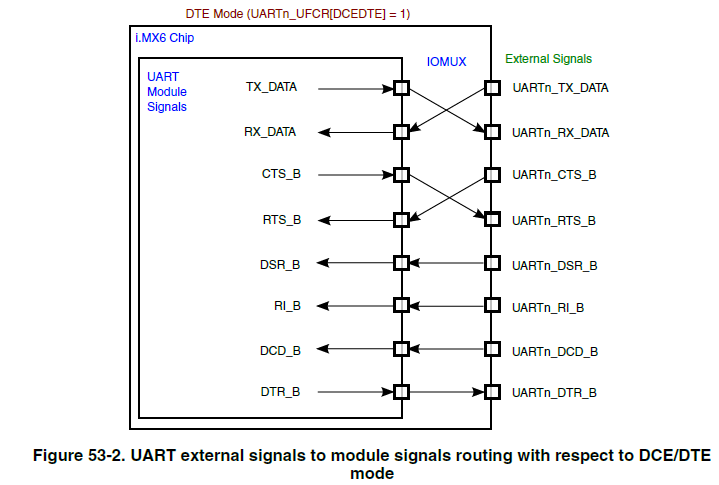

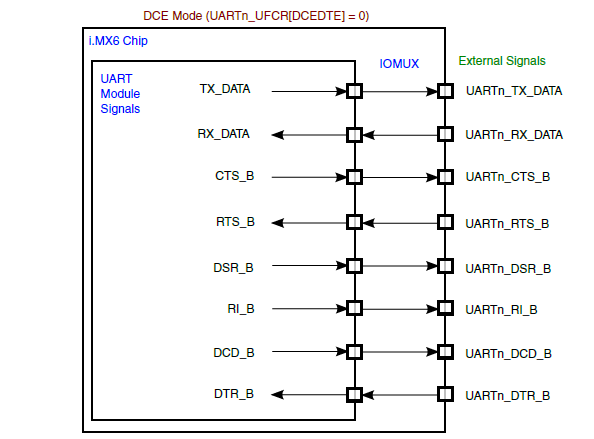

UART设计注意事项:

i.MX的UART有DTE和DCE两种不同的工作模式,他们的信号连接方法是不一样的。

请参考Reference Manual53.2里的描述仔细考虑硬件设计的连接方法。

JTAG设计注意事项:

a. JTAG_MOD – 外部7k ohm电阻下拉到地( GND)。

b. 不要在JTAG_TDO 上连接任何外部上拉或者下拉。

c. JTAG连接器上的JTAG_DE ( 20 pin 模式的第17脚)一定要上拉,这个是JTAG的使能管脚,这个信号在我们i.MX6UL的CPU上是没有的,但是在

连接器上是必须的,对于那些只设计预留,没有20针连接器的客户来说,要确保预留这个信号的上拉。

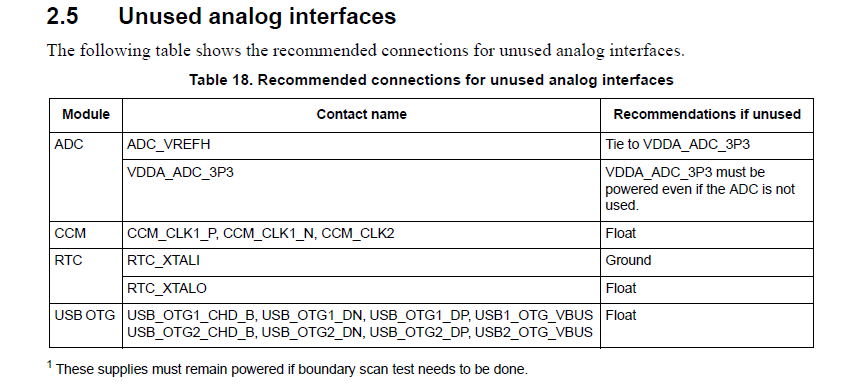

不使用的管脚的连接方法

请参考IMX6ULHDG.pdf这个文档里“Unuse analog interface”表格。

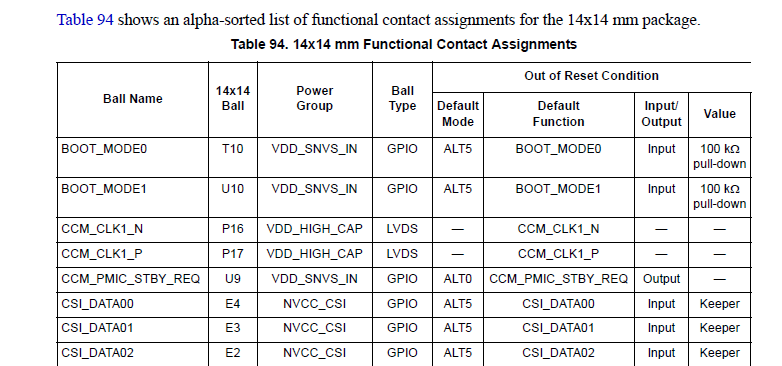

i.MX6UL管脚的默认状态

请参考在i.MX6UL datasheet这个文档里。

Functional Contact Assignments 表格

PCB设计的阻抗控制注意事项:

- 一般的单端线请使用50 ohm阻抗。

- DDR CLK/DQS差分对 请使用100 ohm阻抗。

- USB_DP/DM差分对请使用90 ohm阻抗。

请注意: 所有的这些差分对等长控制需要控制在+/-5mil,走线上需要换层时要同时。