碳化硅 (以下简称“SiC”) 是制造大功率器件最有前景的半导体材料之一,具有出色的物理特性。基于SiC的器件具有高饱和电子漂移速度、高热导率和高击穿电场,相较Si MOSFET, 基于SiC器件 的系统能以更小的尺寸实现更低的损耗和更快的开关速度。

品质和可靠性方法

安森美(onsemi)的工程师编写了一份白皮书《碳化硅材料的征服之旅》,介绍从设计到量产过程中所采用的质量和可靠性方法,包括缜密的设计方法、严格的生产监控、制造控制、充分的筛选和稳健的认证计划,以应对开发基于 SiC 的半导体器件的独特挑战。安森美品质声明/政策充分体现了这种方法。

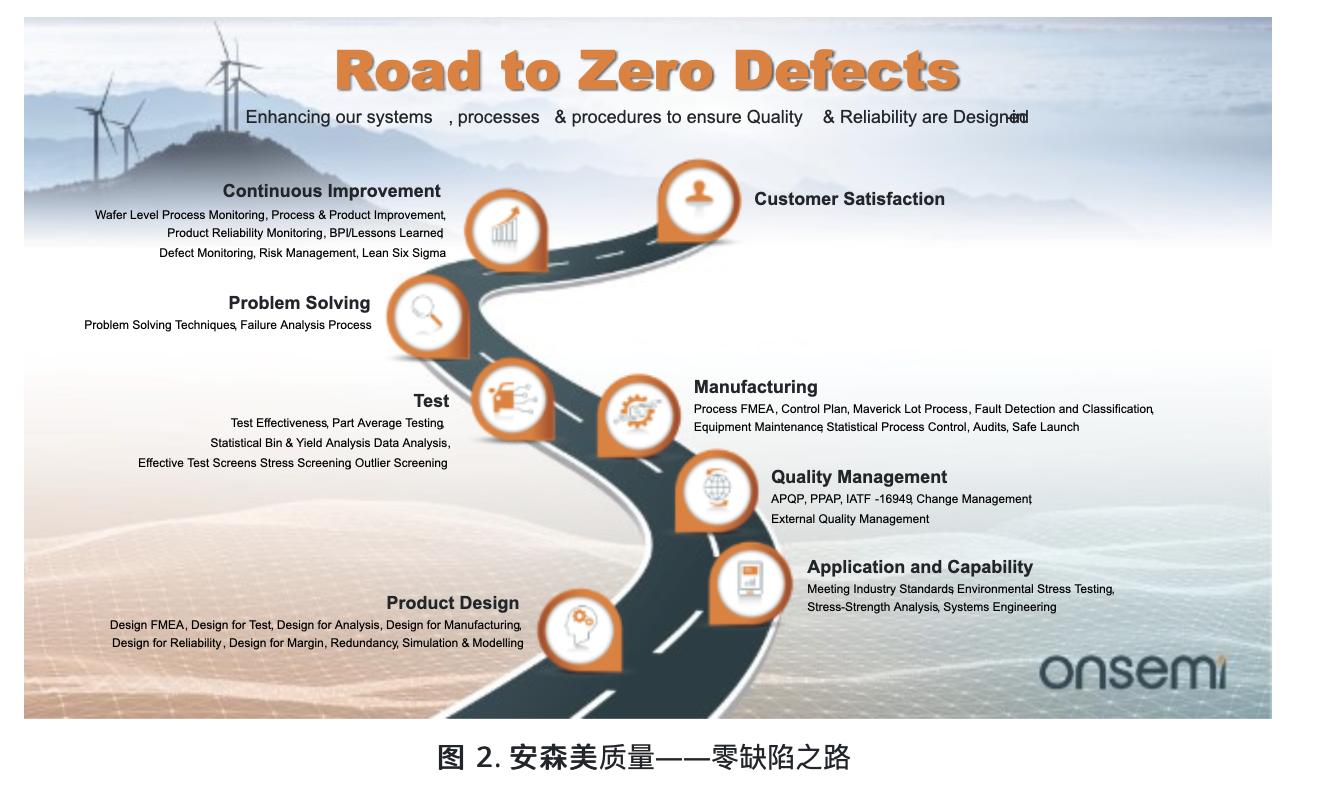

即使产品设计在高可靠性范围内,仍然可能会存在一些与制程相关的可靠性问题。为了消除这些风险,我们必须了解限制性故障模式和机制,然后,我们通过故障的分析和反馈追溯至工艺薄弱点,并采取永久性的纠正措施。安森美在一般可靠性规范中简述了这些程序的使用方法,如以下海报“安森美的质量——零缺陷之路”所示(图2)。

SiC挑战

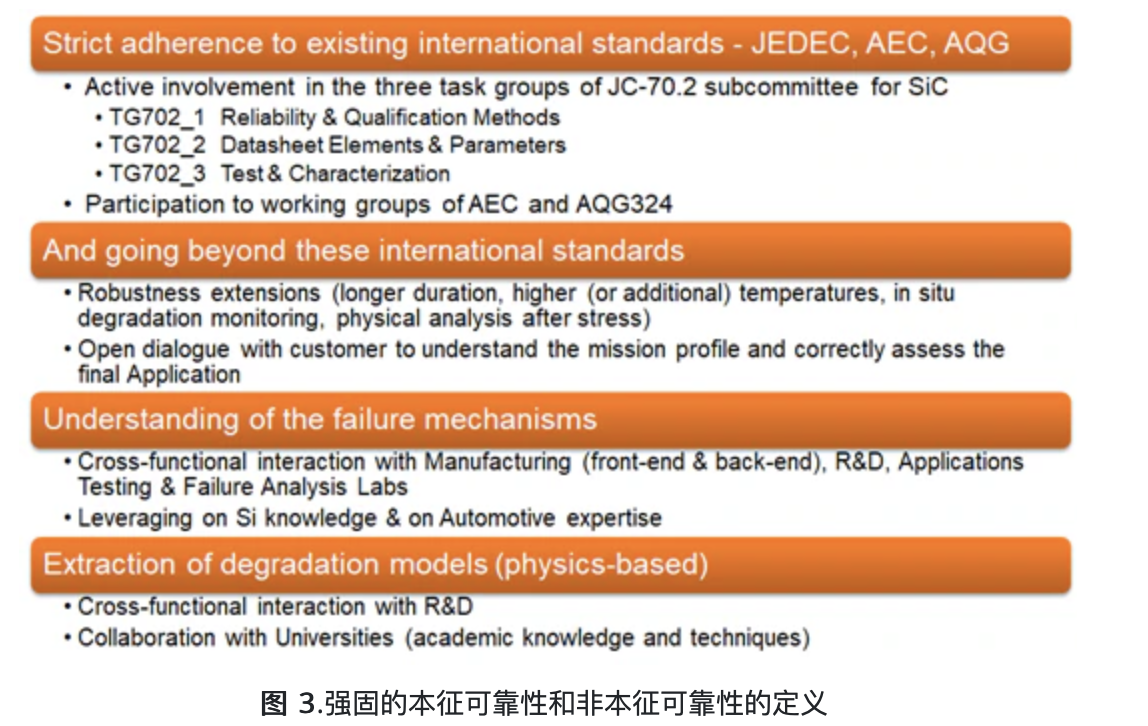

SiC材料兼具出色的物理属性和极具吸引力的设计特性,为研制大功率器件提供了具吸引力的解决方案,但我们必须在设计和制造中考虑如何解决一些挑战。这有助于在客户任务配置文件和应用程序要求方面实现卓越的可靠性和稳健性。必须兼顾多个关键要素,才能成功和安全地将半导体产品投放市场(图 3 )。

虽然硅基半导体技术的国际标准已经确立,但基于SiC的全球方法仍在制定中。JEDEC、AEC 和 AQG 委员会内的多个小组正致力为 SiC 标准奠定基础,以应对第一个挑战。

第二个SiC技术挑战集中在基于物理性质实现对故障机制的理解,以将材料性能与客户应用(从汽车到工业自动化等)的稳健性要求和可靠性要求相匹配。这些挑战包括:

- 衬底和外延的缺陷水平

- 栅极氧化物:本征寿命建模(SiC/SiO2 界面表征)和非本征粒子数(筛选)

- 体二极管退化

- 高压阻断 (HTRB) 期间的可靠性

- 与应用相关的性能(雪崩强固性、边缘端接、短路、宇宙射线耐受性、高 dv/dt 耐受性设计、浪涌电流)

对于每种退化机制,安森美所采取的解决方案都是严格且跨职能的,包括以下步骤:控制 - 改进 - 测试和筛选 - 表征 - 验证和提取模型。

安森美认为与大学和研究中心的密切合作至关重要,有助于安森美对半导体材料进行更深入的理论研究,并获取一些半导体行业可能不具备的专用技术和补充技能。

这白皮书介绍了安森美最近进行的深入研究,重点专注于解决以下对半导体构成关键挑战的问题:

- 偏置温度不稳定性 (BTI)

- 体二极管退化

- 动态应力

评论